# Ferroelectric behavior and NCFETs -TCAD Simulation

Naimah Binti Darmis, AHM Zahirul Alam\*, Muhaimin Bin Mohd Hashim

Department of Electrical and Engineering, International Islamic University Malaysia, Kuala Lumpur, Malaysia

\*Corresponding author: zahirulalam@iium.edu.my

(Received: 14<sup>th</sup> January 2021; Accepted: 27<sup>th</sup> February 2021)

*Abstract*— With the miniaturization of transistors, the current leakage also increases due to the increasing tunnelling effect. Plus, Boltzmann's tyranny limits the subthreshold swing to be best and ideal at 60 mV/decade. Due to these, the power consumption in transistors keeps soaring up. Therefore, in this paper, the Negative Capacitance Effect Field Transistor (NCFET) is discussed as it possesses excellent potentials in reducing the power consumption in transistors. The negative capacitance induced in NCFET enables the internal voltage amplification and reduces the required voltage for the transistor to operate, and therefore, the power consumption is reduced. The literature reviews are done to gain knowledge on the structure and behavior of the NCFET. Next, the process and device simulation of NMOS are studied using Silvaco TCAD to get the idea of developing a circuit simulator model of NCFET. After that, we developed the circuit model of NCFET and MOSFET. Next, the ferroelectric parameters are varied to study how it will affect the ferroelectric material's polarization and capacitance. The ferroelectric thickness and source-drain doping concentration of the proposed NCFET model is also varied to study the NCFET behaviors in peak current, subthreshold slope, saturation current and saturation slope. Lastly, the performances of NCFET and MOSFET are compared. It is found that the NCFET has better performance as compared to the MOSFET as the NCFET can achieve a steeper subthreshold slope.

Keywords: MOSFET, NCFET, Subthreshold slope, Ferroelectric, TCAD

## **1. INTRODUCTION**

The power consumption issue has merged to become a significant concern in CMOS technology. The Negative Capacitance Field Effect Transistor (NCFET) introduced in 2008 by S. Salahuddin is a promising candidate for solving the issue [1]. The negative capacitance exhibits by the ferroelectric in NCFET enables the voltage gate applied to be amplified, thus reducing the power consumption while maintaining the transistor's performance. The negative capacitance is utilized to overcome the Boltzmann mechanics that limit the subthreshold swing at 60 mV/decade. Many NCFET related works have been conducted to study the NCFET performance under different conditions [2-6].

Over the last few decades, shrinking the transistor is one of the implemented alternatives to achieve higher speed, improved power consumption and integration density [7]. However, after considering the conflicts mentioned above, it is worth mentioning that merely downsizing the transistors is no longer applicable. This is where the Negative Capacitance Field-Effect-Transistor (NCFET) is discovered to be one of the promising solutions to solve the issues.

In this paper, ferroelectric behavior and NCFETs behavior will be analyzed using TCAD simulation to observe the devices' performance.

## 2. BACKGROUND OF NEGATIVE CAPACITANCE

И

Electrostatic energy density in a dielectric material is given by

$$v = \int_0^D E(D) dD \tag{1}$$

where E is the electric field and D is the electric displacement field. The relationship between E and D can be

either linear or nonlinear. The total energy stored in a capacitor is given by

$$w = \int_0^Q V(Q) dQ \tag{2}$$

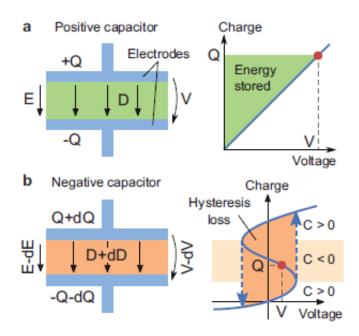

Where *V* is the applied voltage and *Q* is the charge stored in electrodes. The stored energy can be shown in Fig. 1a for a linear positive capacitance, C=dQ/dV, and energy stored in a capacitor is given by  $w = CV^2/2$ . However, for negative capacitance (NC) material, *Q* and *V* are not linear for all applied voltage, as shown in Fig. 1(b). Capacitor with negative differential capacitance dQ/dV < 0 due to dD/dE < 0.

Fig. 1. (a) Positive and (b) Negative capacitances C-V characteristics [8].

### 2.1 Ferroelectric negative capacitance to reduce subthreshold swing

MOSFET with simple capacitance divider as shown in Fig. 2.  $V_G$  is the applied gate voltage,  $C_{ox}$  and  $C_S$  are the oxide and semiconductor capacitance, respectively.

Fig. 2. A simplified view of a MOSFET as a capacitive divider.

The surface potential  $\psi_s$  is related to gate voltage as

$$\psi_s = \frac{c_{ox}}{c_{ox} + c_s} V_G \tag{3}$$

The surface potential and gate voltage is denoted by "body factor", m and is given by

$$m^{-1} = \frac{\delta \psi_s}{\delta V_G} = \left(1 + \frac{C_s}{C_{ox}}\right)^{-1} \tag{3}$$

The subthreshold slope (SS) is defined as  $\delta V_G / \delta \log_{10}(I_D)$  which can be written as

$$SS^{-1} = \frac{\delta log_{10}(I_D)}{\delta V_G} \frac{\delta log_{10}(I_D)}{\delta \psi_s} \frac{\delta \psi_s}{\delta V_G} = \frac{1}{log_{10}} \frac{q}{k_B T} \frac{1}{1 + \frac{C_s}{C_{0x}}}$$

(4)

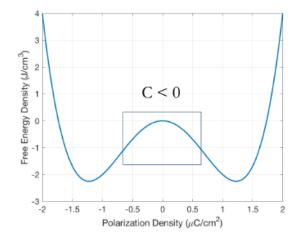

It can be seen that the functional form of m and SS, negative oxide capacitance amplifies the surface potential relative to the gate voltage, thus reducing the body factor below m and reducing SS slope below 60mV/decade. Ferroelectric materials are used to realized negative capacitance. A ferroelectric is defined as a material that exhibits a spontaneous polarization that can be reversed with an applied electric field. The polarization characteristics of ferroelectric materials are shown in Fig. 3.

Fig. 3. Polarization density of ferroelectric material with a distinct negative capacitance zone.

Recently, researchers capture an image of negative capacitance in action [9]. They have shown fundamental, atomistic insight into the physics of negative capacitance. They have shown NC behavior in  $SrTiO_3/PbTiO_3$  heterostructure system.

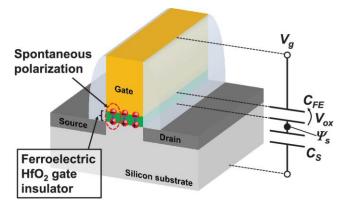

## 2.2 NCMOSFET

Fig. 4 shows the realization of NCMOSFET proposed by Kobayashi et al. and shows the performance of the device. The structure of a NCFET is the same as a MOSFET, except that the gate insulator is replaced by a ferroelectric material, as shown in Fig. 4.

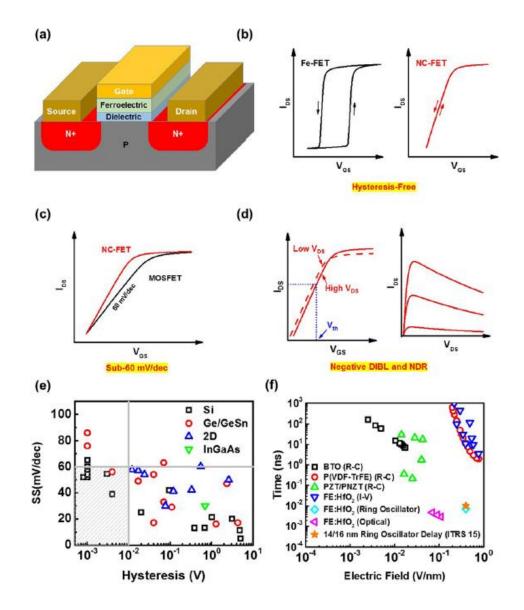

Alam *et al.* recently critically review the progress on negative capacitance [11]. He has summarized the findings in Fig. 5.

Fig. 5. (a) Schematic image of a NC-FET with ferroelectric and conventional dielectric as the gate stack. (b) The fundamental difference in transfer characteristics of a Fe-FET versus a NC-FET which has an anti-clockwise hysteresis or zero hysteresis, respectively. (c) Expected steep-slope less than 60 mV/dec at room temperature for a NC-FET. (d) Expected negative DIBL and negative drain resistance for a NC-FET. (e) Summary of the reported representative data in the literature in terms of SS versus hysteresis in transfer characteristics (SiGe/GeSn, 2D, InGaAs). SS is plotted as the larger SS in forward and reverse gate sweeps and only when both are available. Data without explicitly reported hysteresis are plotted with 1mV hysteresis. (f) Summary of reported switch times of representative ferroelectric films versus the electric field by different characterization methods in the literature (BTO (R-C), PZT/PNZT (R-C), P(VDF-TrFE) (R-C), FE:HfO2 (I-V), FE:HfO2 (ring oscillator), FE:HfO (optical)) [11].

The author also mentioned different types of experiments to support negative capacitances.

# 3. RESULTS AND DISCUSSION

# 3.1 The Ferroelectric Behavior

To characterize the proposed NCFET model, it is important to first acknowledge the behavior of the ferroelectric based on its parameters' variation. There are four ferroelectric parameters which are the electric field  $(E_c)$ , permittivity (*esf*), spontaneous polarization (*P<sub>s</sub>*) and remnant polarization (*P<sub>r</sub>*). Figures 6-9 show the capacitance and polarization vs gate bias with varied *esf*, *P<sub>s</sub>*, *P<sub>r</sub>* and *E<sub>c</sub>*, respectively.

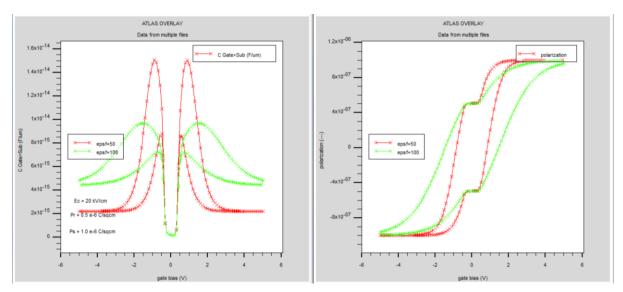

Fig. 6. The capacitance and polarization vs gate bias for esf = 50 and esf = 100

Figure 6 shows the capacitance and the ferroelectric polarization curve when the *esf* parameter is varied at 50 and 100, while other parameters are made constant ( $P_r = 0.5 \mu C/cm^2$ ,  $P_S = 1 \mu C/cm^2$ ,  $E_c = 20 \text{ kV/cm}$ ). The figure shows that the 100-*esf* ferroelectric exhibits higher capacitance and thinner hysteresis loop as compared to that of 50-*esf* ferroelectric.

Fig. 7. The capacitance and polarization vs gate bias for  $P_S = 1 \mu C/cm^2$  and  $P_S = 5 \mu C/cm^2$

Figure 7vshows the capacitance and the polarization curve of the ferroelectric when the Ps parameter is varied

at  $1\mu$ C/cm<sup>2</sup> and  $5\mu$ C/cm<sup>2</sup>, while other parameters are made constant (*esf* = 50, *P<sub>r</sub>*=  $1\mu$ C/cm<sup>2</sup>, *E<sub>c</sub>* = 20 kV/cm). From the figure, it can be concluded that as the *P<sub>s</sub>* parameter increases, the ferroelectric capacitance also increases, and the hysteresis loop becomes smaller.

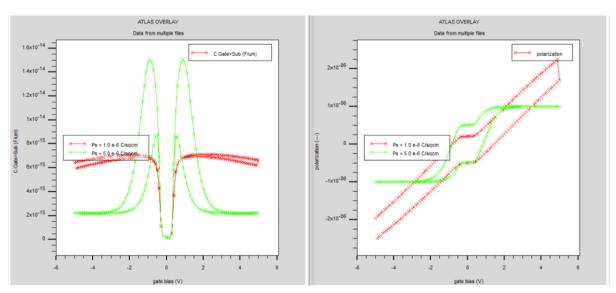

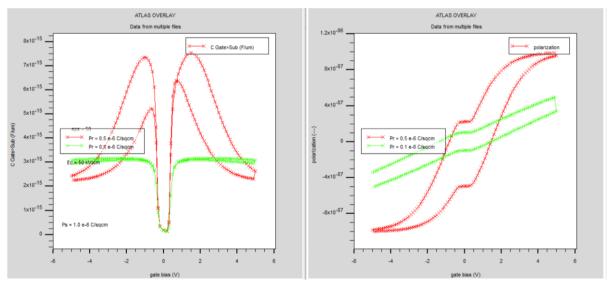

Fig. 8. The capacitance and polarization vs gate bias for  $P_r = 0.5 \mu C/cm^2$  and  $P_r = 0.1 \mu C/cm^2$

Figure 8 shows the capacitance and the polarization curve of the ferroelectric when the  $P_r$  parameter is varied at  $0.5\mu$ C/cm<sup>2</sup> and  $0.1\mu$ C/cm<sup>2</sup>, while other parameters are made constant (*esf* = 50,  $P_s$  = 1 $\mu$ C/cm<sup>2</sup>,  $E_c$  = 50 kV/cm). From the figure, it is observed that each different  $P_r$  yields a very different shape of the hysteresis loop and the  $0.5\mu$ C/cm<sup>2</sup>- $P_r$  ferroelectric exhibits much higher capacitance as compared to the  $0.1\mu$ C/cm<sup>2</sup>- $P_r$  ferroelectric.

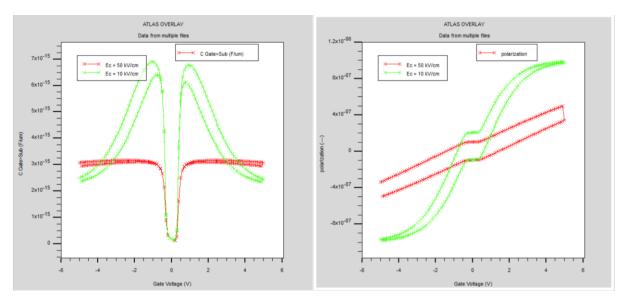

Fig. 9. The capacitance and polarization vs gate bias for  $E_c = 50$  kV/cm and  $E_c=10$  kV/cm

Figure 9 shows the capacitance and the polarization curve of the ferroelectric when the  $E_c$  parameter is varied at 50 kV/cm and 10 kV/cm, while other parameters are made constant (esf = 50,  $P_S = 1\mu$ C/cm<sup>2</sup>,  $P_r = 0.1\mu$ C/cm<sup>2</sup>). From the figure, it is found that the 50 kV/cm- $E_c$  ferroelectric produces a thin hysteresis loop and high capacitance.

In short, the ferroelectric parameters are affecting the capacitance and polarization behavior of the ferroelectric material. Therefore, it is better to choose suitable ferroelectric parameters to achieve a better capacitance matching between the ferroelectric and dielectric capacitor.

# 3.2 The NCFET Structure for TCAD Simulation

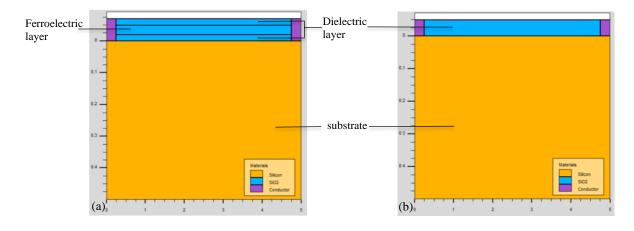

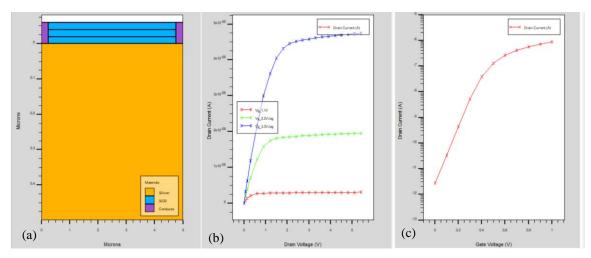

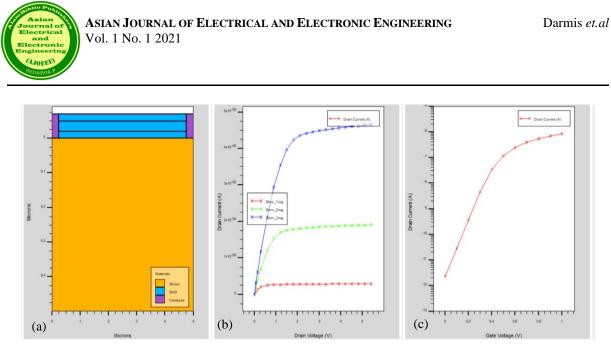

Figure 10 shows the structure of the proposed NCFET compared to MOSFET. The MOSFET consists of two layers, which are the substrate and one dielectric layer, as shown in Figure 4.6a, while the NCFET consists of 4 layers as shown in Figure 4.6b. Table 4.1 lists the NCFET parameters.

Fig. 10. The proposed structure of (a) NCFET and (b) MOSFET.

| Parameter (unit)                                      | NCFET                          |  |  |

|-------------------------------------------------------|--------------------------------|--|--|

| p-well doping concentration (cm <sup>-3</sup> )       | $1x10^{19}$                    |  |  |

| Source-drain doping concentration (cm <sup>-3</sup> ) | $1 x 10^{19}$                  |  |  |

| Substrate doping concentration (cm <sup>-3</sup> )    | 3x10 <sup>16</sup>             |  |  |

| Dimension (µm x µm)                                   | 5x5                            |  |  |

| Gate length, $L_g(nm)$                                | 4.5                            |  |  |

| Dielectric material                                   | SiO <sub>2</sub>               |  |  |

|                                                       | $E_c=1.2$ MV/cm                |  |  |

| Ferroelectric material                                | $Pr=12.5e \mu\text{C/cm}^2$    |  |  |

|                                                       | $Ps = 13.24 \mu \text{C/cm}^2$ |  |  |

|                                                       | <i>esf</i> =35.5               |  |  |

| Dielectric material                                   | SiO <sub>2</sub>               |  |  |

| Dielectric thickness (nm)                             | 0.02                           |  |  |

| Table 1. The  | e proposed NCFET | and MOSFET | parameters. |

|---------------|------------------|------------|-------------|

| 1 4010 1. 111 | proposed iter Li |            | parameters. |

As can be seen from Table 1, the chosen ferroelectric parameters are  $E_c=1.2$ MV/cm,  $P_r=12.5$ e  $\mu$ C/cm<sup>2</sup>,  $P_s=13.24 \mu$ C/cm<sup>2</sup> and *esf=35.5* for our NCFET model. On top of that, both devices' gate length is set to be 4.5nm to avoid any short-channel effect [12].

## 3.1.1 The Effect of Ferroelectric Thickness on the NCFET Performance

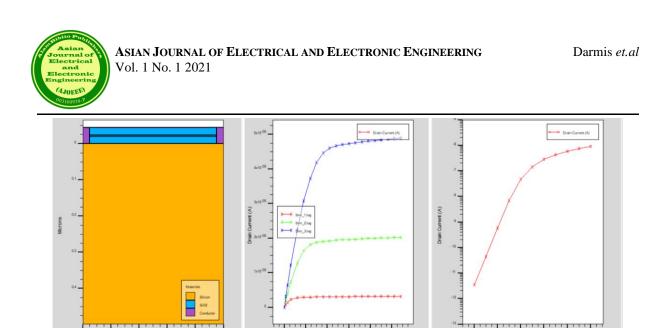

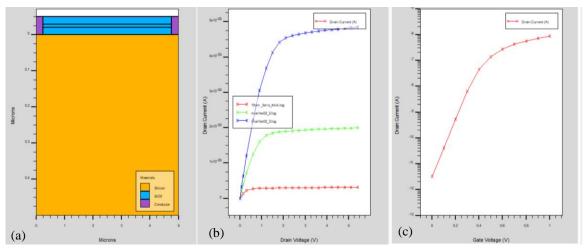

For this set of experiments, the ferroelectric layer's thickness is varied while all other parameters are made fixed, including the source-drain doping concentration of  $1 \times 10^{19} \text{cm}^{-3}$ . The NCFET structures with the different ferroelectric thickness of 5nm, 10nm, 20nm and 30nm, and their I-V characteristics are depicted in Figure 11,12,13 and 14, respectively.

For all the  $I_D$  vs  $V_{DS}$  plot depicted in this project, there are three different applied gate voltages which are 1.1V, 2.2V and 3.3V and their curves are shown by the red, green, and blue curve, respectively. The drain voltage is then supplied until 5.5V with the step of 0.3V. Next, for the  $I_D$  vs  $V_g$  plot, the drain voltage is biased with 0.025V and the gate voltage is ramped from 0 to 1V with the step of 0.1V.

Fig. 11. Variation of drain current,  $I_D$  versus (b) Drain voltage,  $V_{DS}$  (c) Gate voltage,  $V_g$  of **5** nm thick ferro NCFET.

(b)

(a)

(c)

Fig. 12. Variation of drain current,  $I_D$  versus (b) Drain voltage,  $V_{DS}$  (c) Gate voltage,  $V_g$  of 10 nm-thick ferro NCFET.

Fig. 13. Variation of drain current,  $I_D$  versus (b) Drain voltage,  $V_{DS}$  (c) Gate voltage,  $V_g$  of 20 nm-thick ferro NCFET.

Fig. 14. Variation of drain current,  $I_D$  versus (b) Drain voltage,  $V_{DS}$  (c) Gate voltage,  $V_g$  of 30nm-thick Ferro NCFET.

From the results shown in Figure 11 until Figure 14, it shows that all the NCFET with different ferroelectric thickness are following the MOSFET I-V characteristic. Next, the behaviors of the NCFET in terms of peak current, saturation slope, saturation current and subthreshold slope are summarized in Table 2.

| Ferroelectric<br>thickness<br>(nm) | Peak<br>Current<br>(mA) | Saturation<br>Slope<br>(µA/V) | Subthreshold<br>slope with bias<br>drain voltage<br>= 0.025 V<br>(mV/dec) | Voltage<br>Gate (V) | Saturation<br>Current<br>(mA) |

|------------------------------------|-------------------------|-------------------------------|---------------------------------------------------------------------------|---------------------|-------------------------------|

| 5                                  | 0.04889 0.4615          | 0.4615                        | 89.102                                                                    | 1.1                 | 0.003212                      |

|                                    |                         |                               |                                                                           | 2.2                 | 0.020251                      |

|                                    |                         |                               |                                                                           | 3.3                 | 0.048877                      |

| 10                                 | 0.04837                 | 0.4623                        | 89.3754                                                                   | 1.1                 | 0.003147                      |

|                                    |                         |                               |                                                                           | 2.2                 | 0.02                          |

|                                    |                         |                               |                                                                           | 3.3                 | 0.048364                      |

| 20                                 | 0.04742                 | 0.467                         | 89.9125                                                                   | 1.1                 | 0.003031                      |

|                                    |                         |                               |                                                                           | 2.2                 | 0.019542                      |

|                                    |                         |                               |                                                                           | 3.3                 | 0.047424                      |

| 30                                 | 0.0465                  | 0.47366                       | 90.4744                                                                   | 1.1                 | 0.002917                      |

|                                    |                         |                               |                                                                           | 2.2                 | 0.019094                      |

|                                    |                         |                               |                                                                           | 3.3                 | 0.0465                        |

Table 2: The NCFET electrical behaviors with different ferroelectric thickness.

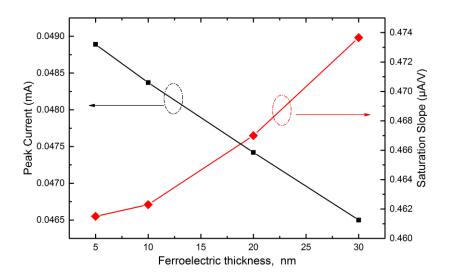

Figure 15 depicts the relationship between the peak current and the saturation slope with the ferroelectric thickness. From the figure, it is found that as the ferroelectric thickness increases, the peak current decreases, whereas the saturation slope is increasing with the ferroelectric thickness, although there is not much difference between the slope values.

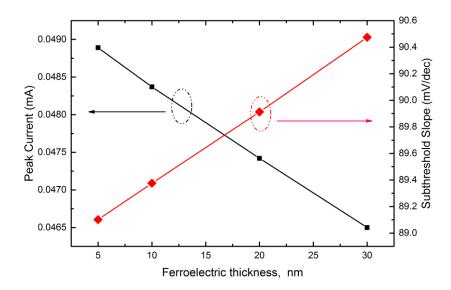

Figure 16 shows the relationship between the subthreshold slope and ferroelectric thickness. The plot shows that the subthreshold slope is directly proportional to the ferroelectric thickness. In terms of subthreshold slope, the best performance is achieved by the 5nm-thick ferroelectric NCFET as it achieves the steepest slope of 89.10mV/dec. As in equation (5), when the ferroelectric thickness ( $T_{FE}$ ) increases, the ferroelectric capacitance ( $C_{FE}$ ) decreases, which makes it closely match the C<sub>MOS</sub>. The enhanced matching between the C<sub>MOS</sub> and the  $C_{FE}(|C_{FE}|-C_{MOS}>0)$  then increases the voltage amplification factor,  $A_G$ . The voltage amplification factor and the subthreshold slope have a negative correlation, which implies that the higher the ferroelectric thickness, the steeper the subthreshold slope.

#### **ASIAN JOURNAL OF ELECTRICAL AND ELECTRONIC ENGINEERING** Vol. 1 No. 1 2021

Darmis et.al

$$C_{FE} = \frac{dQ}{dV_{FE}} = \frac{1}{2\alpha T_{FE}} = \frac{2}{3\sqrt{3}} \frac{P_r}{E_c T_{FE}}$$

$$A_G = \frac{|C_{FE}|}{|C_{FE}| - C_{FEG}}$$

(5)

(6)

$$SS = 60 x \left(1 + \frac{c_{dm}}{c_{ox}}\right) x \frac{1}{A_G}$$

$$\tag{7}$$

Fig. 15. Peak current and the saturation slope vurses ferroelectric thickness

Fig. 16. Subthreshold slope versus ferroelectric thickness.

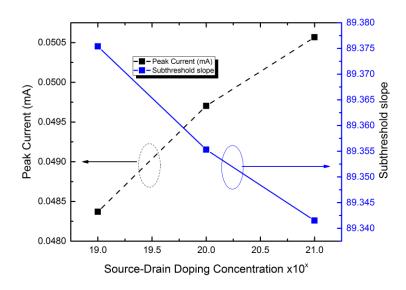

Figure 17 shows the relationship between the peak current and the subthreshold slope with the source-drain doping concentration. The figure shows that the peak current is directly proportional and the subthreshold slope is inversely proportional to the source-drain doping concentration. The higher the doping concentration, the greater the depletion capacitance ( $C_{dm}$ ), the greater the increases in  $C_{dm}/C_{FE}$  as compared to the  $C_{dm}/C_{ox}$ , and thus, the steeper the subthreshold slope. However, noticed that the subthreshold slope, SS is not less than 60 mV/dec as it supposed to be as according to equation (8), the absence of proper fabrication processes and other ignored variables.

$$SS = 60 \ x \ (1 + \frac{c_{dm}}{c_{ox}} - \frac{c_{dm}}{|c_{FE}|})$$

(8)

Where  $C_{dm}$  = Depletion capacitance,  $C_{ox}$  = Gate oxide capacitance

Therefore, it is found that by increasing the source-drain doping concentration in the proposed NCFET model, the subthreshold slope can be made steeper.

Fig. 17. Subthreshold slope vurses source-drain doping concentration.

## 4. CONCLUSION

The effects of ferroelectric parameters (electric field ( $E_c$ ), permittivity (*esf*), spontaneous polarization ( $P_s$ ) and remnant polarization ( $P_r$ )) are studied on its capacitance and polarization behaviors. Next, the structure and parameters of the proposed NCFET is presented. The effects of the ferroelectric thickness and source-drain doping concentration on the proposed NCFET and MOSFET behavior are demonstrated. It is proved that the NCFET has better performance as it achieved a steeper subthreshold slope.

The results show that as the ferroelectric thickness increases, the peak current and the saturation current are decreasing while the saturation slope and subthreshold slope are increasing. Next, in terms of the source-drain doping concentration, the peak current, saturation current, and saturation slope are increasing with the source-drain doping concentration, while the subthreshold slope is inversely proportional to the doping concentration.

## ACKNOWLEDGEMENT

This paper is financially supported by the Ministry of Higher Education Malaysia (MoHE) through the Research Centre, International Islamic University Malaysia under the Fundamental Research Grant Scheme (FRGS), Ministry of Higher Education, Malaysia (FRGS/1/2018/TK04/UIAM/01/2).

#### REFERENCES

- S. Salahuddin and S. Datta (2008) Can the subthreshold swing in a classical FET be lowered below 60 mV/decade? Tech. Dig. Int. Electron Devices Meeting. pp. 693–696. https://doi.org/10.1109/IEDM.2008.4796789

- [2] Wang, H., & Wang, H. (2017). A Two-Terminal Active Capacitor. IEEE Transactions on Power Electronics, 32(8), 5893-5896. https://doi.org/10.1109/tpel.2017.2668764

- [3] Catalan, G., Jiménez, D., & Gruverman, A. (2015). Negative capacitance detected. Nature Materials, 14(2), 137–139. https://doi.org/10.1038/nmat4195

- [4] Z. C. Yuan et al. (2016) Switching-Speed Limitations of Ferroelectric Negative-Capacitance FETs, IEEE Transactions on Electron Devices, vol. 63, no. 10, pp. 4046-4052. https://doi.org/10.1109/TED.2016.2602209

- [5] Bilal, B., Ahmed, S., & Kakkar, V. (2018). An Insight into Beyond CMOS Next Generation Computing using Quantum-dot Cellular Automata Nanotechnology. International Journal of Engineering and Manufacturing, 8(1), 25-37. https://doi.org/10.5815/ijem.2018.01.03

- [6] Jo, J., Choi, W. Y., Park, J.-D., Shim, J. W., Yu, H.-Y., & Shin, C. (2015). Negative Capacitance in Organic/Ferroelectric Capacitor to Implement Steep Switching MOS Devices. Nano Letters, 15(7), 4553–4556. d https://doi.org/10.1021/acs.nanolett.5b01130

- [7] Ko, E., Shin, J., & Shin, C. (2018). Steep switching devices for low power applications: negative differential capacitance/resistance field effect transistors. Nano Convergence, 5(1). d https://doi.org/10.1186/s40580-018-0135-4

- [8] Michael Hoffmann, Franz Paul Gustav Fengler, Benjamin Max, Uwe Schroeder, Stefan Slesazeck, and Thomas Mikolajick (2019). Negative Capacitance for Electrostatic Supercapacitors. Adv. Energy Mater. 9: 1901154. https://doi.org/10.1002/aenm.201901154

- [9] Yadav, A.K., Nguyen, K.X., Hong, Z. et al. (2019). Spatially resolved steady-state negative capacitance. Nature 565: 468–471. https://doi.org/10.1038/s41586-018-0855-y

- [10] Masaharu Kobayashi, Toshiro Hiramoto (2016). On device design for steep-slope negativecapacitance field-effect-transistor operating at sub-0.2V supply voltage with ferroelectric HfO2 thin film. AIP Advances, 6(2). https://doi.org/10.1063/1.4942427

- [11] Muhammad A. Alam, Mengwei Si, and Peide D. Ye (2019) A critical review of recent progress on negative capacitance field-effect transistors Appl. Phys. Lett. 114, 090401. https://doi.org/10.1063/1.5092684

- [12] Cheng-I Lin, C., Khan, A. I., Salahuddin, S., & Hu, C. (2016). Effects of the Variation of Ferroelectric Properties on Negative Capacitance FET Characteristics, IEEE Transactions on Electron Devices, Vol 63 No. 5, pp- 2197 – 2199. https://doi.org/10.1109/TED.2016.2514783